五金工業(yè)的多元應(yīng)用 從機(jī)器配件到化工原料

五金工業(yè)作為制造業(yè)的重要組成部分,涵蓋了廣泛的產(chǎn)品領(lǐng)域,包括Ruicheng五金零部件、機(jī)器金屬配件、沖壓產(chǎn)品、服裝金屬配件以及化工原料及相關(guān)產(chǎn)品。這些產(chǎn)品不僅服務(wù)于傳統(tǒng)制造業(yè),還深入到了服裝、化工等多元行業(yè),展現(xiàn)出強(qiáng)大的應(yīng)用潛力。

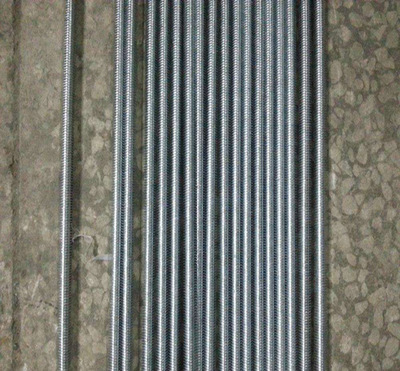

Ruicheng五金零部件以其精密制造和耐用性著稱,廣泛應(yīng)用于機(jī)械設(shè)備、建筑結(jié)構(gòu)和家用產(chǎn)品中。例如,在自動(dòng)化生產(chǎn)線中,這些零部件確保了機(jī)器的穩(wěn)定運(yùn)行,提升了生產(chǎn)效率。同時(shí),機(jī)器金屬配件作為核心組件,支持著各種工業(yè)設(shè)備的運(yùn)轉(zhuǎn),從簡(jiǎn)單的緊固件到復(fù)雜的傳動(dòng)部件,都體現(xiàn)了金屬材料的強(qiáng)度和可塑性。

沖壓產(chǎn)品則通過(guò)先進(jìn)的沖壓工藝,制作出形狀各異的金屬件,如汽車(chē)零部件和電子外殼。這種工藝高效且成本低,適合大規(guī)模生產(chǎn),滿足了現(xiàn)代工業(yè)對(duì)標(biāo)準(zhǔn)化和快速交付的需求。在服裝行業(yè),金屬配件如紐扣、拉鏈和裝飾扣件,不僅增強(qiáng)了服裝的功能性,還融入了時(shí)尚元素,提升了產(chǎn)品的美學(xué)價(jià)值。這些配件通常采用耐腐蝕材料,確保在頻繁使用中保持美觀。

化工原料及產(chǎn)品在五金工業(yè)中扮演著關(guān)鍵角色,例如金屬表面處理用的涂料和防銹劑,這些化工材料能延長(zhǎng)金屬產(chǎn)品的壽命并改善其性能。從原料供應(yīng)到成品應(yīng)用,整個(gè)鏈條體現(xiàn)了五金行業(yè)的多學(xué)科交叉特性,推動(dòng)了技術(shù)創(chuàng)新和產(chǎn)業(yè)升級(jí)。

Ruicheng五金零部件、機(jī)器金屬配件、沖壓產(chǎn)品、服裝金屬配件以及化工原料及產(chǎn)品的綜合應(yīng)用,不僅促進(jìn)了制造業(yè)的發(fā)展,還拓展到日常生活的方方面面。未來(lái),隨著新材料和智能化制造的興起,這一領(lǐng)域?qū)⒗^續(xù)演化,為全球市場(chǎng)提供更高效、環(huán)保的解決方案。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.yingvision.cn/product/11.html

更新時(shí)間:2026-04-27 11:53:08